1. 들어가기 전에

I2C는 필립스에서개발한 직렬 버스 입니다. 1992년에 1.0이 발표 되었고 현재 대부분의 디바이스는 1.0 규격을 준수하고 있습니다. 1998년도에 버전 2.0이 발표 되었고, 2.0에 새롭게 추가 된 것은 "high-speed mode"로써 3.4 Mbit/s 속도를 지원 합니다. 최신 핸드폰에 사용되는 AP를 위한 PM-IC와 같이 아주 소수 디바이스에서만 high-speed mode를 지원 합니다.

I2C는 UART 통신과 같이 아주 간단한 구성과 2개의 라인을 사용하는 점에서 같으나, UART 통신은 1:1 통신을 지원하나, I2C는 그림-1과 같이 N(마스터):N(슬레이브)을 지원 합니다. 다만, 대부분 1(마스터):N(슬레이브)로 I2C-BUS를 구성 합니다.

I2C-BUS에서 마스터를 포함하여 동일한 버스에 최대 112개의 노드를 연결 할 수 있으나 보통은 많아야 5 ~ 6개를 초과하지 않습니다.

2000년대 초반에는 I2C의 특허 문제로 인하여 I2C의 프로토콜과 아주 미묘한 차이로 인하여 MCU의 GPIO로 소프트웨어 I2C를 구현하여 통신을 해야 했으나, 현재는 특허가 해제되어 대부분의 디바이스는 표준 프로토콜을 지원하여 최근에는 하드웨어 I2C를 사용 합니다.

가. I2C 통신 속도

최근의 대부분 I2C를 지원하는 디바이스는 fast-speed mode를 지원 합니다. I2C 프로토콜에는 I2C-BUS에 서로 다른 속도가 다른 디바이스를 연결할 수 있지만, MCU에서 대부분 고정된 속도를 지원하기 때문에 별도의 분리된 버스를 사용 합니다.

- low-speed mode : 100 kbit/s

- fast-speed mode : 400 kbit/s

- high-speed mode : 3.4 Mbit/s

나. I2C 통신 방식

I2C는 반2중 통신방식(half-duplex)을 지원하기 때문에 송신자가 데이터를 송신하고 있으면 수신자는 데이터를 수신만 할 수 있고, 수신자는 송신을 할 수 없습니다. 이는 반대로 수신자가 송신자에게 데이터를 송신하는 경우에는 송신자가 데이타를 보낼 수 없습니다.

2. I2C-BUS 내부 구조

I2C-버스의 내부 구조를 알아보기 전에 약간의 전자공학 지식이 필요 합니다. BJT(Bipolar Junction Transister)와 MOSFET에 대한 이해를 갖고 있어야 합니다.

2.1. 오픈 컬렉터(open collector) 와 오픈 드레인(open drain)

BJT를 사용하면 open collector이고 모스펫(MOSFET)을 사용하면 open drain 입니다. 이 둘은 소자만 다르고 원리는 같습니다. 최근 IC의 경우 모스펫(MOSFET)을 주로 사용 합니다.

왼쪽 그림에서 게이트(gate, base)는 전등을 켜는 스위치와 같습니다. 게이트(gate, base)의 스위치를 켜면 드레인(drain, collector)은 로우(LOW, 0 V) 상태가 됩니다. 역으로 게이트(gate, base)의 스위치를 끄게 되면 드레인(drain, collector)은 알 수 없는 상태(high impedance)가 됩니다. 드레인(drain, collector)이 열려 있어서 오픈(open)이라고 불리고 여러 개의 디바이스(장치)를 하나의 선으로 연결하여 양방향 통신을 할 수 있는 회로 기술 입니다.

가. 오픈 드레인(open drain) 회로

그림-3은 오픈 드레인(open-drain)을 여러 디바이스(장치)으로 연결을 하면 양방향으로 통신을 할 수 있는 장점과 디바이스 간 레벨(level, voltage)이 다른 경우에도 통신이 가능하며 풀업 저항(pull-up register)을 하나로 회로를 간단하게 만들 수 있는 장점이 있습니다.

디바이스는 게이트(gate)를 켜면 드레인과 소스(source)가 연결되어 그라운드(ground)에 연결되어 드레인(drain)은 로우(LOW, 0V) 상태가 됩니다. 게이트(gate)를 끄면 드레인과 소스 간 연결이 끊기고 드레인은 외부 풀업 저항과 연결되어 하이(HIGH, VDD) 상태가 됩니다.

그림-4는 Device #1이 게이트(gate)를 통해 드레인(drain)에 연결된 라인의 상태를 제어하는 예이고,

그림-5는 Device #2가 제어를 하는 예 입니다.

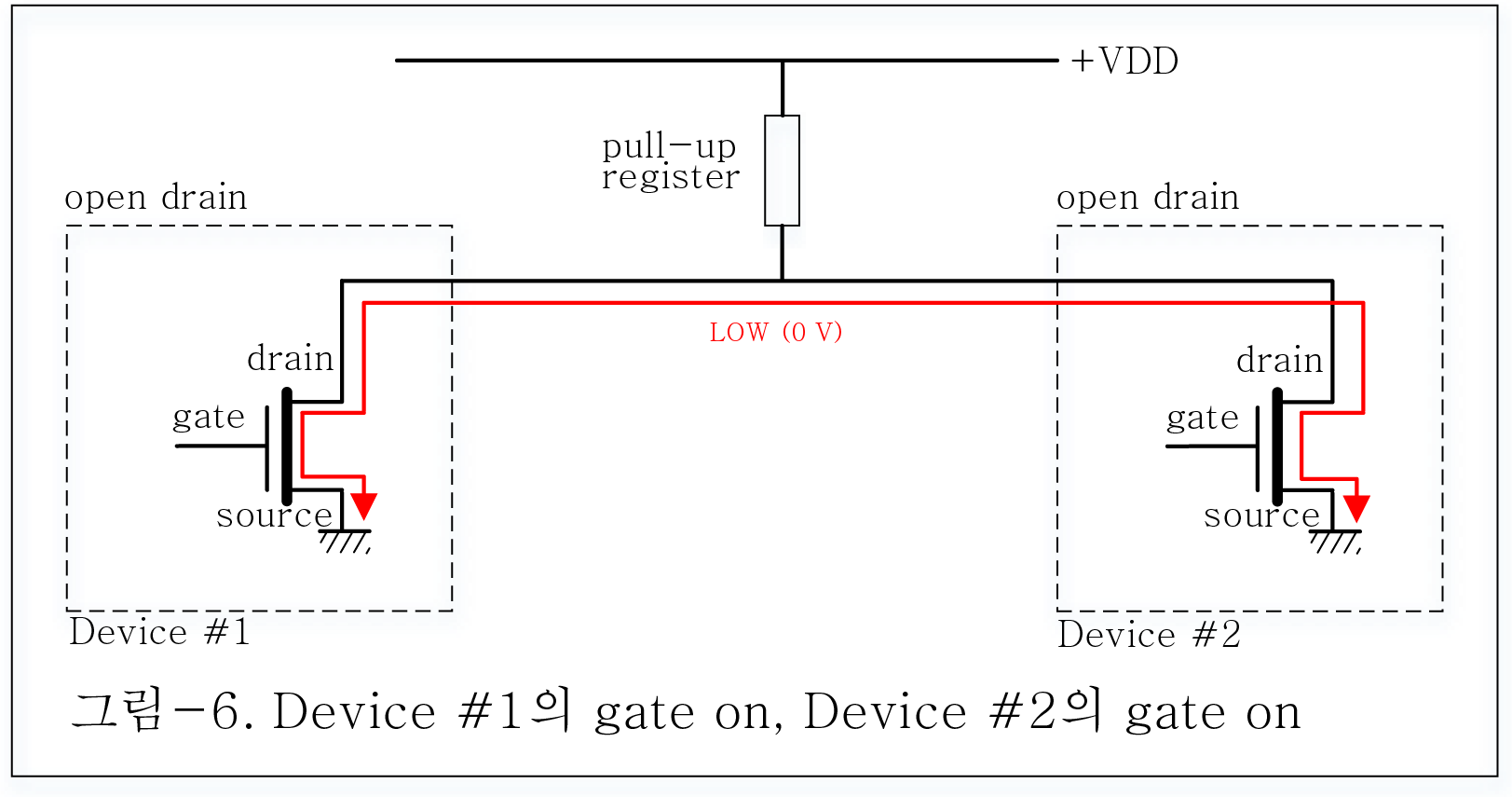

그림-6은 Device #1과 Device #2가 동시에 드레인(drain)을 제어하는 경우로써 같이 제어를 하게 되면 문제가 됩니다. 만약 Device #1의 게이트(gate)을 켜서 드레인(drain)을 로우(LOW) 상태로 유지 한 경우 Device #2는 게이트(gate)를 켜든 끄든 항상 로우(LOW) 상태로써 제어가 되지 않습니다. 그러므로 동시에 게이트(gate)를 제어하면 안됩니다.

2.2. I2C-BUS와 오픈 드레인(open drain)

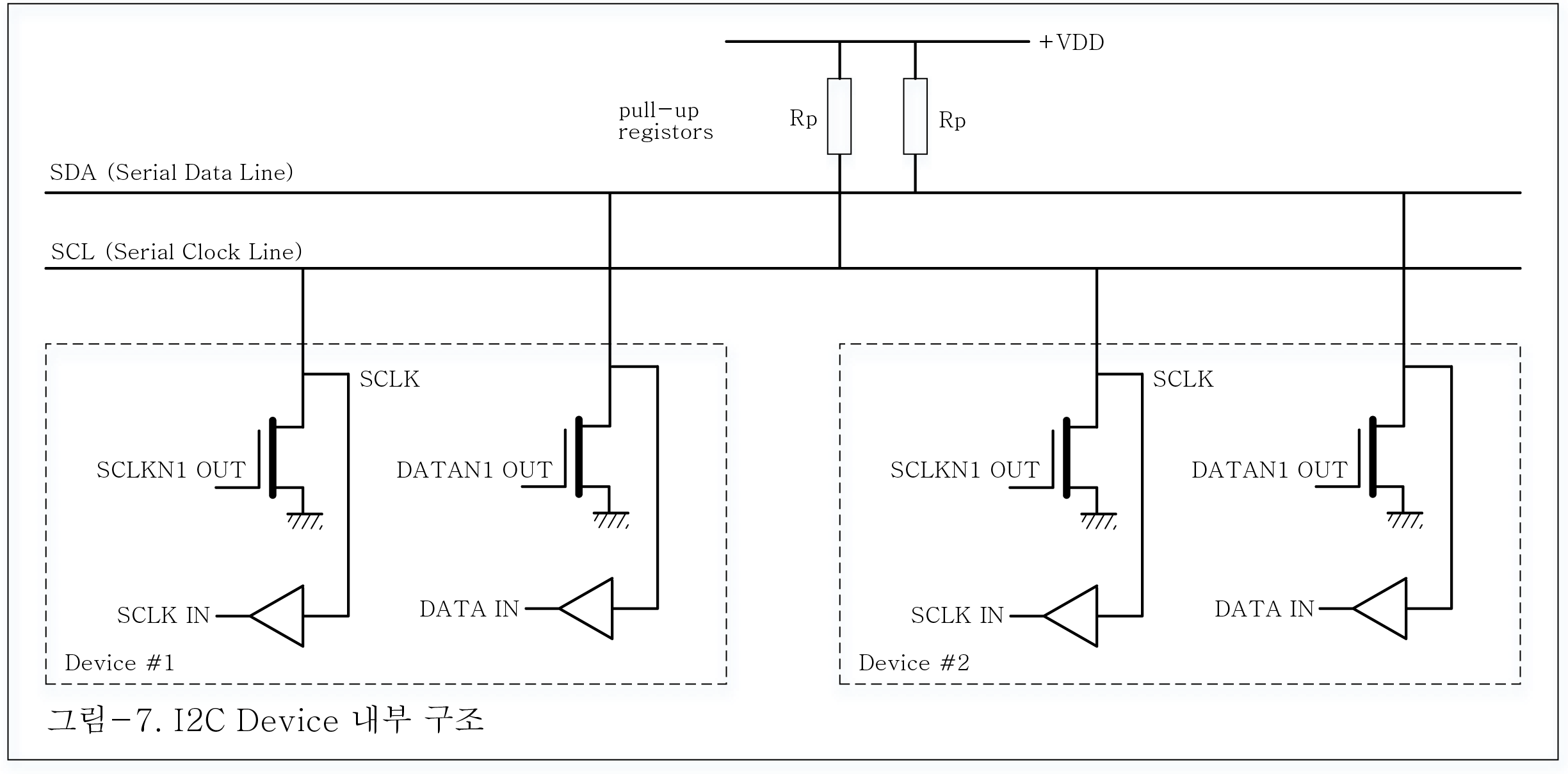

그림-7은 SCL과 SDA의 오픈 드레인(open drain)을 보여 줍니다. Device #1에서 I2C-BUS의 권한을 획득 했다면 SCLKN1 OUT과 DATAN1 OUT를 통해 SCL과 SDA를 제어 합니다. Device #2에서는 SCLKN1 OUT과 DATAN1 OUT을 끄고(off) SCLK IN과 DATA IN을 통해 SDA와 SCL의 값을 읽습니다.

만약 외부 Rp(풀업 레지스터)가 없다면 Device #2에서 SCL과 SDA에 로우(LOW, 0V) 값은 알 수 있지만 하이(HIGH, VDD) 상태일 때는 값을 읽을 수 없습니다. 그러므로 I2C-BUS에 풀업 저항을 연결하지 않으면 통신을 할 수 없습니다.

오픈 드레인(open drain)에서 설명했듯이 I2C-BUS의 SDA와 SCL은 두 개의 디바이스(장치)가 쓰기를 시도하면 안됩니다. 그래서 I2C-BUS에서는 마스터(master)가 먼저 쓰기를 합니다.

I2C-BUS에서 멀티 마스터(master)인 경우에 마스터는 SDA와 SCL의 라인이 일정 시간 이상 하이(HIGH) 상태를 유지할 때 마스터는 I2C-BUS에 쓰기 가능한 상태로 판단을 하고 쓰기를 시도 합니다. 다만, 대부분 I2C-BUS에는 한 개의 마스터와 다 수의 슬레이브로 구성을 합니다.

2.3. I2C-BUS에서의 +VDD

I2C에서 로우(LOW)와 하이(HIGH)의 레벨(level, voltage)은 다음과 같은 범위를 같습니다.

- LOW : 0V ~ VDD*0.3

- HIGH : VDD*0.7 ~ VDD

만약 VDD가 3.3V면 LOW는 0V ~ 0.99V이고 HIGH는 2.31V ~ 3.3V 입니다. VDD가 5.0V면 LOW는 0V ~ 1.5V이고 HIGH는 3.5V ~ 5V 입니다.

위 기준 레벨은 I2C 규격에 정의되어 있는 값이고 대부분 칩도 같은 값이나, 정확한 값은 사용하는 칩의데이터시트를 확인 해야 합니다.

가. 마스터 동작 전압이 3.3V이고 슬레이브 동작 전압이 3.3V

마스터와 슬레이브 모두 동작 전압이 3.3V이기 때문에 I2C-BUS의 +VDD 전압은 3.3V로 하면 됩니다.

나. 마스터 동작 전압이 3.3V이고 슬레이브 동작 전압이 5.0V

레벨 쉬프트(level-shift) 칩을 사용하지 않는 이상 직접 연결을 하여 통신을 할 수 없습니다. 다만, 특정 칩의 경우에 가능 합

니다.

I2C 풀업 저항의 +VDD가 3.3V 일 때

이 경우 마스터는 동작하는데 문제가 없으나 슬레이브는 HIGH를 인식 하는 레벨이 3.5V(5V*0.7) ~ 5.0V이기 때문에 슬레이브에서는 HIGH를 인식할 수 없어 사용을 할 수 없습니다.

I2C 풀업 저항의 +VDD가 5.0 일 때

이 경우에는 마스터가 허용하는 입력 전압을 데이터시트를 통해 확인을 해야 합니다. 대부분의 MCU나 AP(Application Processor)는 허용 전압 범위 밖에 있어 연결하는 순간 MCU나 AP가 망가 집니다. 다만, ST사의 STM32 MCU에는 아두이노 주변장치를 위해 I2C의 SCL과 SDA에 5V 전압을 허용 합니다. 이 경우에는 I2C의 +VDD를 5.0으로 통신을 할 수 있습니다.

다. 마스터 동작 전압이 5.0V이고 슬레이브 동작 전압이 3.3V

슬레이브의 입력 허용 전압이 5.0V이면 직접 연결을 할 수 있으나, 대부분은 직접 연결을 허용하지 않습니다. 이런 경우에는 레벨 쉬프트(level-shift, 3.3V->5.0V and 5.0V->3.3V)를 사용해야 합니다.

3. I2C-BUS 프로토콜

3.1. 비트(bit) 전송

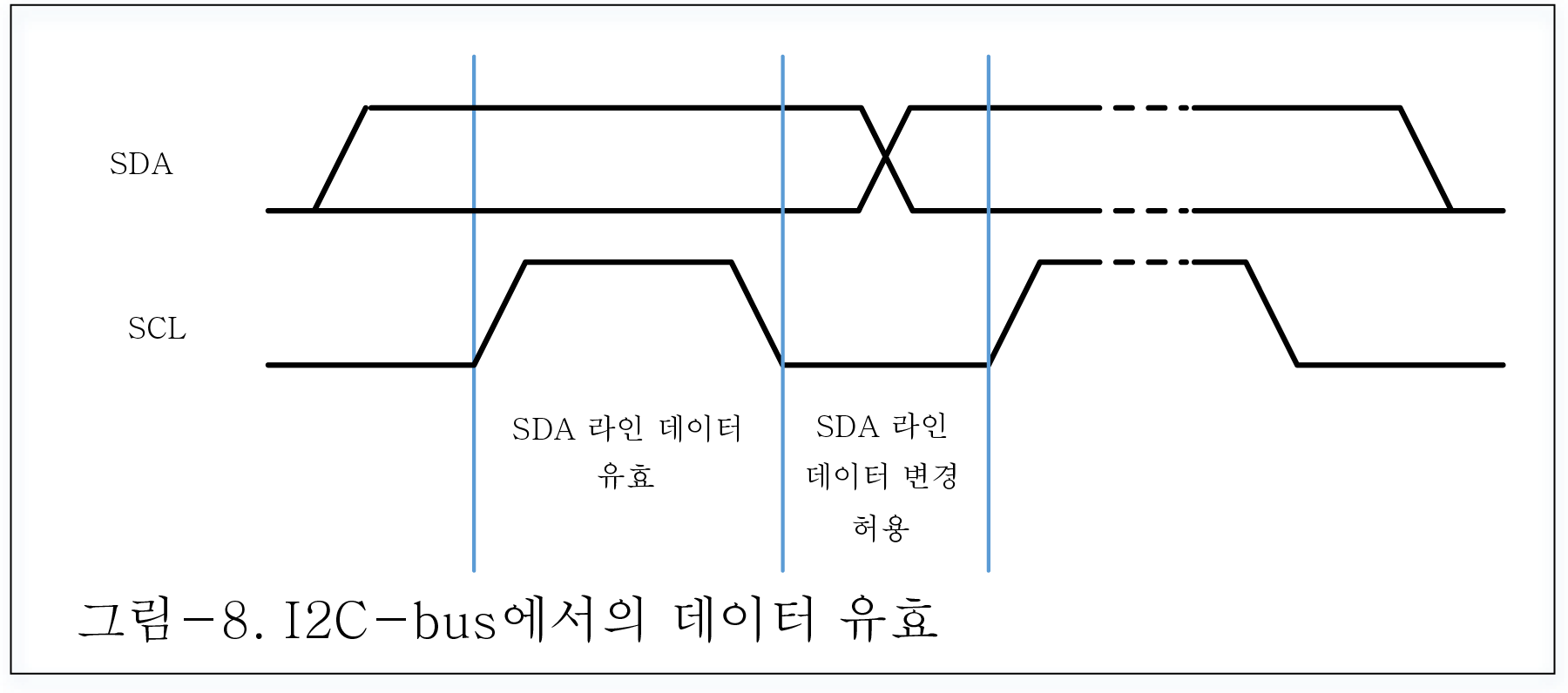

I2C-버스는 SCL 라인에 클럭을 출력하고 SDA 라인을 통해 비트(bit) 단위로 데이터를 출력 합니다. 그림-8과 같이 수신자(receiver)는 SCL의 상승 에지(rising edge) 후에 SDA에서 데이터를 읽으면 되고, 송신자(transmitter)는 SCL의 하강 에지(falling edge) 후에 SDA에 보낼 데이터를 쓰면 됩니다.

3.2. START와 STOP 상태

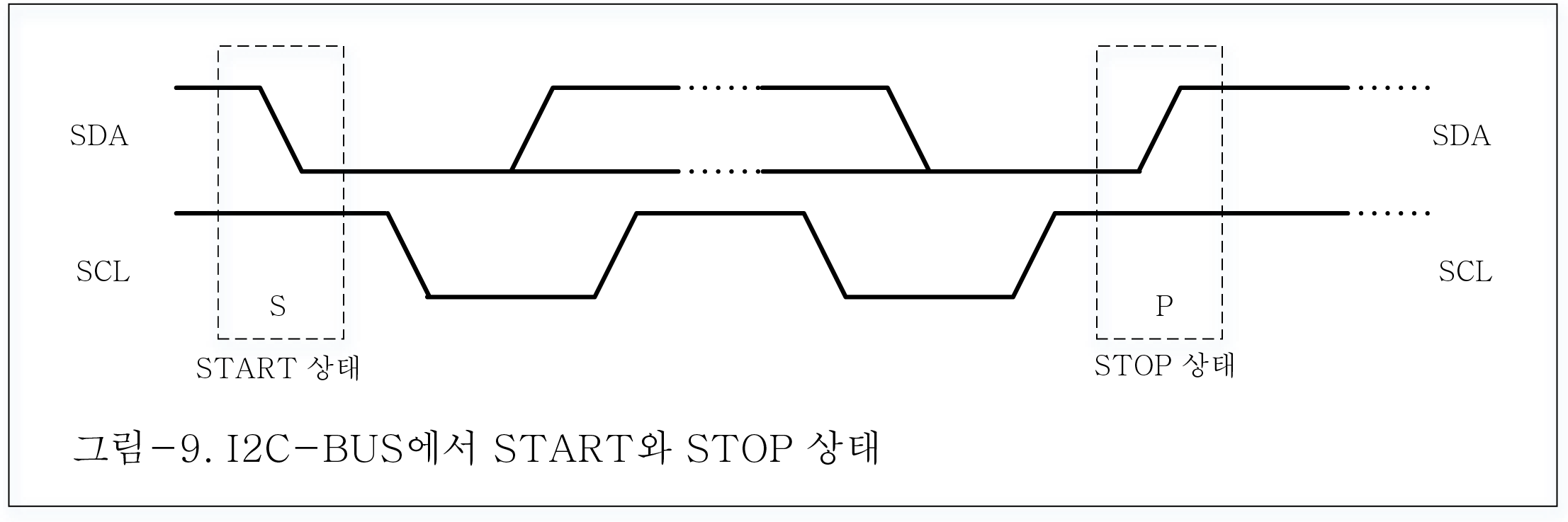

그림-9는 I2C-BUS에서 데이터를 전송하기 시작(START)과 데이터를 전송을 끝내는(STOP) 상태가 있습니다. 시작(START)과 종료(STOP)은 마스터만 할 수 있고, 슬레이브는 시작(START) 상태를 감지하여 통신 준비를 합니다. 만약 다중 마스터 모드이면 마스터는 시작(START) 상태를 감지하면 I2C-BUS가 사용 중임으로 데이터 전송을 시도하면 안되며 종료(STOP) 상태를 감지 한 후에 시도를 해야 합니다.

3.3. 데이터 전송

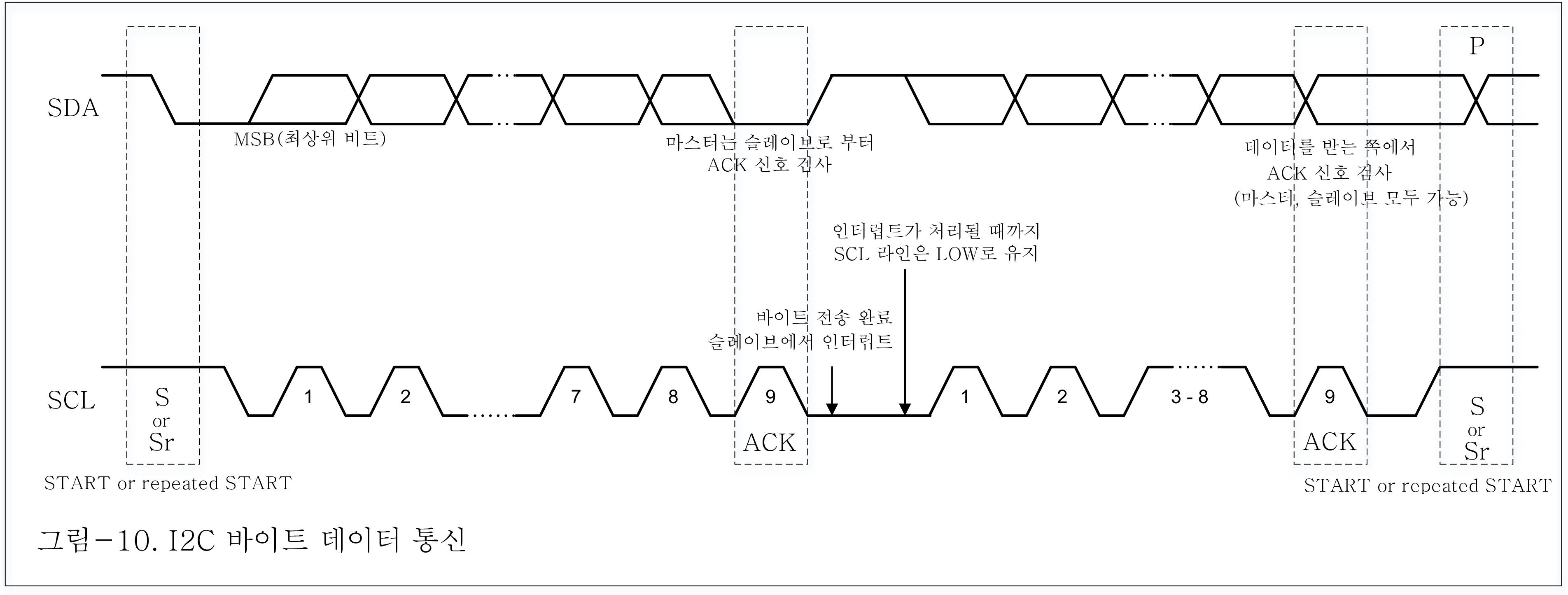

가. 바이트 포맷

그림-10은 I2C 데이터 통신 입니다. SDA 라인에 데이터는 항상 8비트(1 바이트) 길이를 가지며 한 번에 보낼 수 있는 데이터의 길이는 제한이 없습니다. 1 바이트 전송당 1 비트의 승인(acknowledge) 비트를 가져야 합니다. 데이터는 최상위 비트(MSB)부터 전송을 합니다.

슬레이브는 데이터를 수신할 수 없거나 전송을 할 수 없는 경우, 슬레이브는 클럭라인 SCL 라인을 강제로 로우(LOW)를 유지하여 마스터를 강제로 대기 상태로 만들 수 있습니다. 슬레이브는 다음 데이터 전송을 준비되면 클럭 라인 SCL을 해제 하면, 마스터는 그 이후에 계속 할 수 있습니다. 정상적인 데이터 전송 시에 슬레이브는 SCL 클럭을 입력 받고 SCL 라인은 항상 마스터가 관리 합니다. 슬레이브가 SCL를 강제로 로우(LOW)로 유지를 할 수 있는 것은 오픈 드레인(open drain)의 게이트(gate)를 켜면 SCL 라인이 로우(LOW)로 유지하게 되고, 더 이상 유지 할 필요가 없으면 게이트(gate)를 끄면 됩니다.

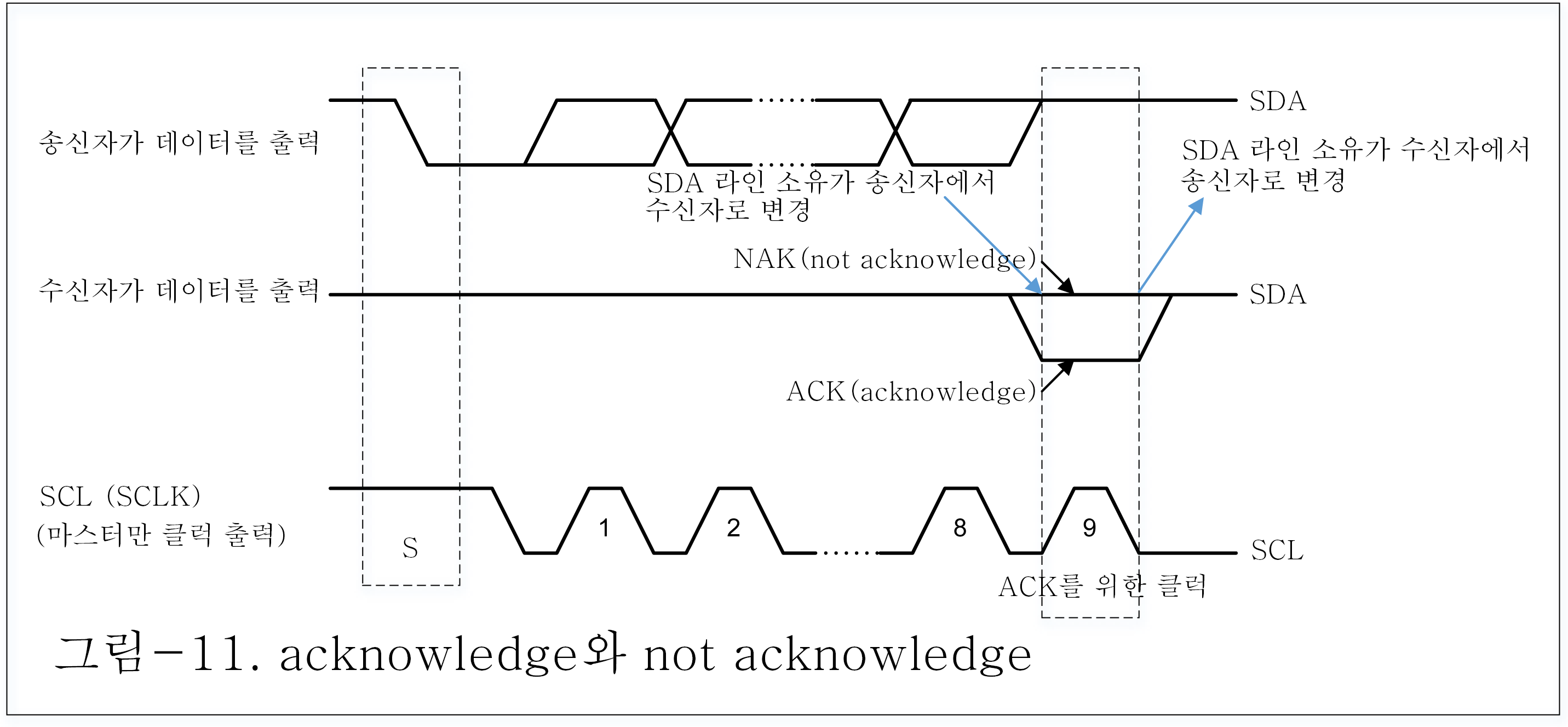

나. 승인 (acknowledge)

데이터 전송 시에 승인(acknowledge)비트는 필수 사항 입니다. 데이터 전송 및 승인 비트를 위한 클럭(SCL)은 마스터가 1바이트 데이터를 위해 8개의 클럭을 발생하고, 그 다음에 승인 비트를 위한 1개의 클럭을 발생 합니다. 송신기(transmitter)는 승인 비트 클럭을 라이징 에지(rising edge) 전에 SDA 라인을 하이(HIGH, 송신기의 SDA에 있는 오픈 드레인(open drain)의 게이트(gate)를 꺼야 합니다.)로 상태를 변경 합니다. 수신기(receiver)는 승인 비트 클럭의 상승 에지(rising edge) 후에 SCL 라인이 하이(HIGH) 상태 동안 SDA 라인을 로우(LOW, 수신기의 SDA에 있는 오픈 드레인(open drain)의 게이트(gate)를 켭니다.)로 유지를 합니다. SCL에서 하강 에지(falling edge)에서 슬레이브는 오픈 드레인(open drain)의 게이트(gate)를 끔니다.

간단하게 정리하면 9번째 클럭에서 수신자(receiver)는 SDA 라인을 로우(LOW)로 유지를 합니다.

다. 비 승인(not acknowledge)

NACK는 승인 비트 클럭 동안 SDA 라인을 하이(HIGH) 상태 입니다. 송신기(transmitter)가 데이터를 전송 한 후에 수신기에서 ACK(acknowledge)를 받지 못하는 상태가 NACK 상태로써 수신기가 데이터를 제대로 받지 못하는 경우 입니다. 슬레이브가 NACK로 응답하는 경우는 다음과 같습니다.

- 슬레이브 주소가 일치하는 슬레이브가 존재하지 않을 때

- 슬레이브가 어떤 문제가 발생하여 통신을 하지 못하는 경우

정상적으로 NACK로 응답을 하는 경우는 다음과 같습니다.

- 마스터가 슬레이브에 데이터 읽기에서 더 이상 데이터를 읽을 필요가 없을 때 NACK로 응답을 슬레이브에 주면 슬레이브는 더 이상 응답을 하지 않고 종료를 합니다.

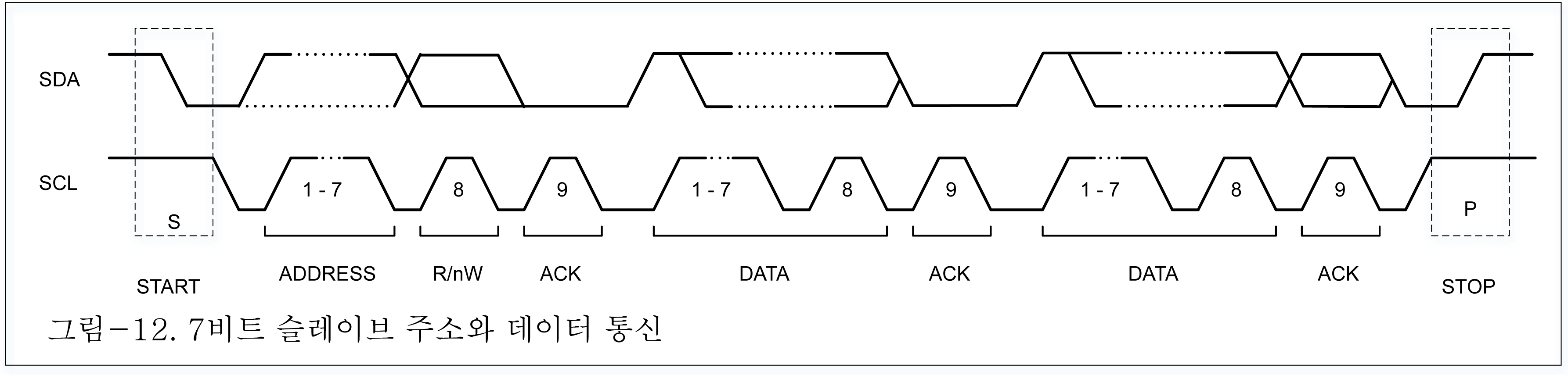

3.4. 7비트 슬레이브 주소

슬레이브 주소는 7비트 주소와 10비트 주소가 있으나 거의 대부분 7비트 주소를 사용 합니다. 슬레이브 주소는 7비트이나 I2C의 데이터 전송은 바이트(8비트) 단위로써 그림-12.에서와 같이 1 바이트의 길이를 갖습니다. 그래서 어떤 자료에서는 슬레이브 주소를 표현할 때 8비트로 표현을 하는 경우도 많습니다. 1 바이트에는 슬레이브 주소 7비트와 읽기/쓰기 플래그 1 비트를 더해서 8비트가 됩니다.

가. 읽기 (read)

읽기는 마스터에서 슬레이브로부터 데이터를 읽기 입니다. 읽기/쓰기 1비트 플래그 값은 1 입니다.

나. 쓰기 (write)

쓰기는 마스터에서 슬레이브에 데이터를 씁니다. 읽기/쓰기 1비트 플래그 값은 0 입니다.

3.5. 데이터 통신

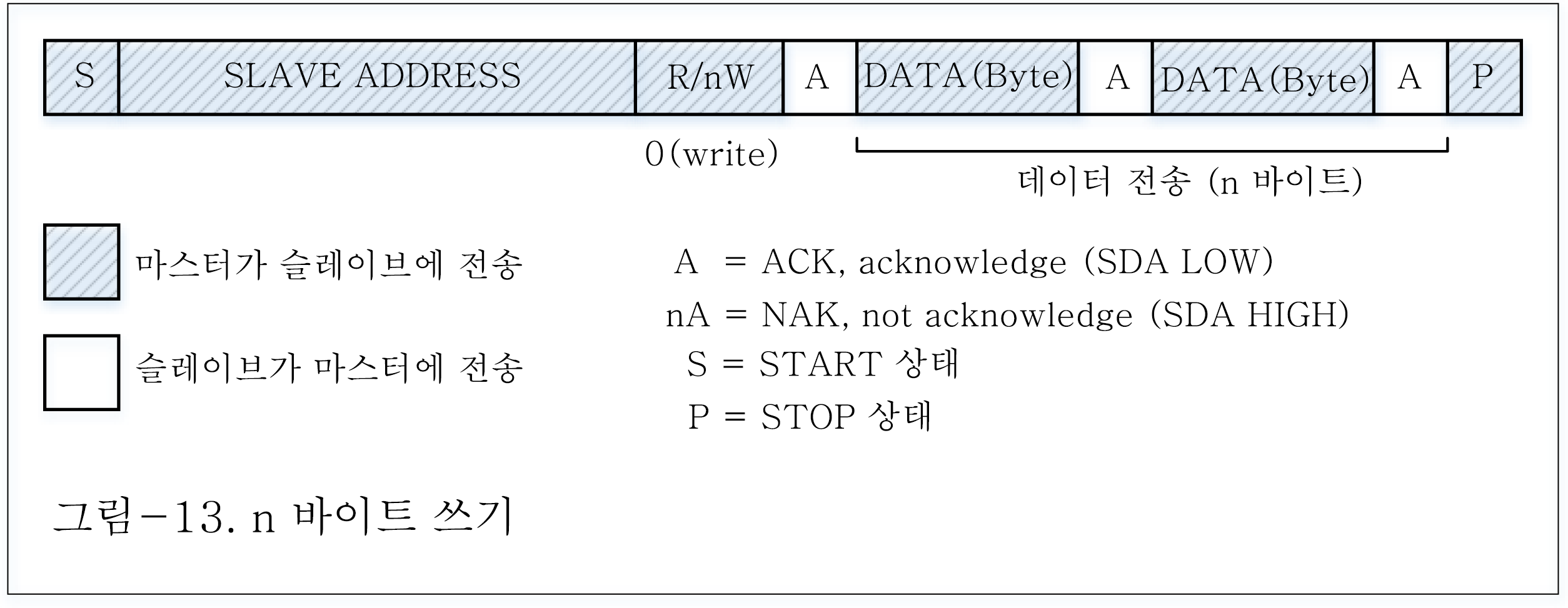

가. 데이터 쓰기(write)

그림13은 I2C-BUS에서 마스터가 슬레이브에 데이터를 쓰는 예 입니다. 첫 번째 바이트에는 7비트 슬레이브와 쓰기 플래그(0)을 슬레이브에 보내면 슬레이브는 자신의 7비트 주소와 비교를 하여 같으면 ACK(승인 비트, SDA LOW)를 마스터에 보냅니다. 마스터는 ACK를 받지 않으면 I2C-BUS에 STOP를 보내고 종료하고, ACK를 받으면 데이터 전송을 합니다.

마스터는 1 바이트를 보내고 ACK를 받으면 다음 1 바이트를 보냅니다. 마스터는 더 이상 보낼 데이터가 없으면 STOP 명령을 보내고 종료 합니다.

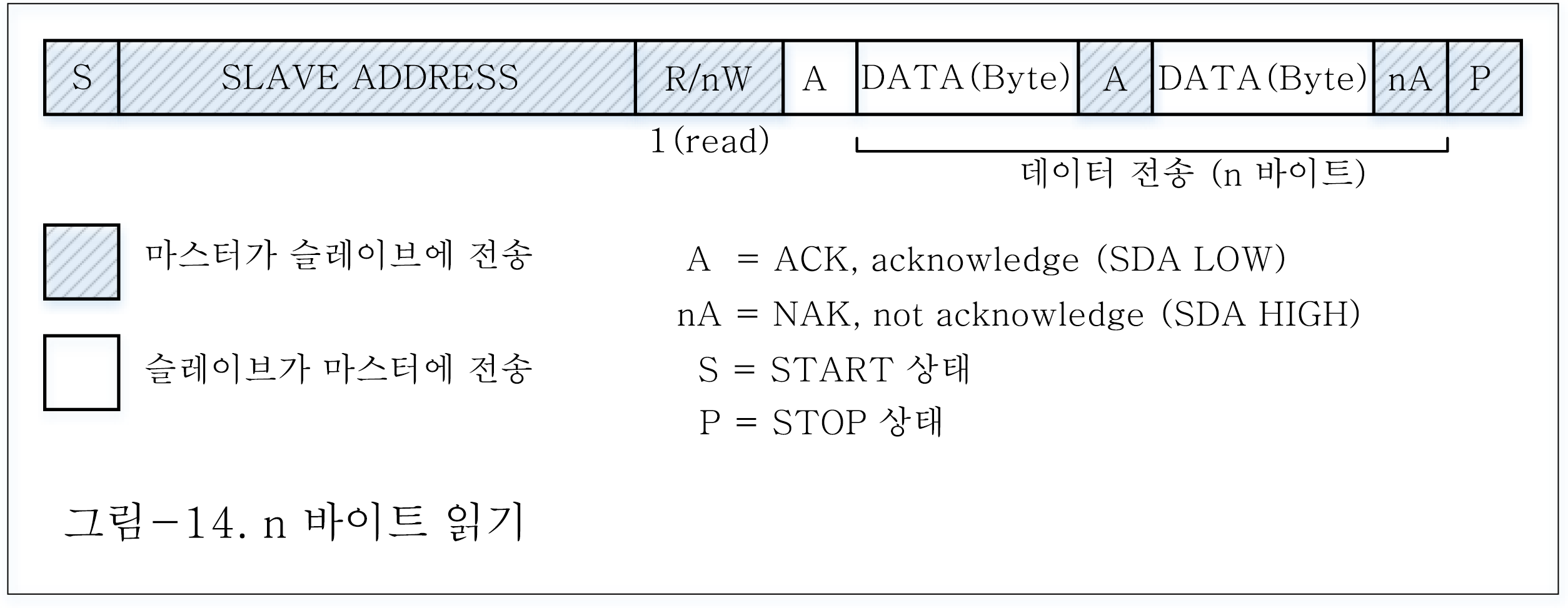

나. 데이터 읽기(read)

그림14은 I2C-BUS에서 마스터가 슬레이브에 있는 데이터를 읽는 예 입니다. 첫 번째 바이트는 데이터 쓰기와 같이 슬레이브 7비트 주소와 슬레이브에 데이터를 읽기 플래그(1)을 보냅니다.

마스터는 1 바이트를 읽고 ACK를(SDA LOW)를 슬레이브에 보내면 계속 읽기를 하겠다는 의미이고 마스터가 더 이상 읽을 필요가 없으면 NAK(SDA HIGH)를 보내면 슬레이브는 더 이상 데이타를 마스터로 보내지 않습니다.

'로봇 이야기 > interface' 카테고리의 다른 글

| PWM (Pulse Width Modulation) (0) | 2022.12.07 |

|---|---|

| I2C-BUS 활용 (0) | 2022.12.06 |

댓글